[뉴스토마토 오세은 기자] 전 세계 파운드리 시장 점유율 1위인 대만 TSMC 추격에 나선

삼성전자(005930) (72,800원 ▼700원 -0.96%)가 앞으로 격차를 좁힐 수 있는 주요 핵심 기술은 ‘패키징’이 될 것으로 관측됩니다. 패키징은 각기 다른 반도체를 한데 묶어 칩셋처럼 작동하게 만드는 기술입니다. 애플, 엔비디아 등 내로라하는 반도체 기업들이 AI 반도체 열풍에 올라타기 위해 경제성은 갖추되 빠른 시간 안에 성능을 높일 수 있는 칩을 공급받기 원하면서 첨단 패키징 기술을 가진 TSMC를 찾고 있습니다. 삼성전자가 첨단 패키징 분야에서 기술력을 확보하면 HBM 시장은 물론 고객사 유치에도 탄력이 붙을 것이란 분석입니다.

19일 업계에 따르면 애플, 엔비디아, 인텔 등 글로벌 반도체 기업들이 TSMC의 첨단 패키징 기술인 ‘칩 온 웨이퍼 온 서브스트레이트(Chip on Wafer on Substrate·CoWoS)’ 2.5D를 활용한 제품 출시를 예고했습니다. 애플은 당장 올 하반기에 출시할 아이폰16 시리즈에 TSMC의 ‘CoWoS’를 활용한 애플리케이션 프로세서(AP) A18 바이오닉을 탑재하기 위해 최근 TSMC와 계약을 체결했습니다.

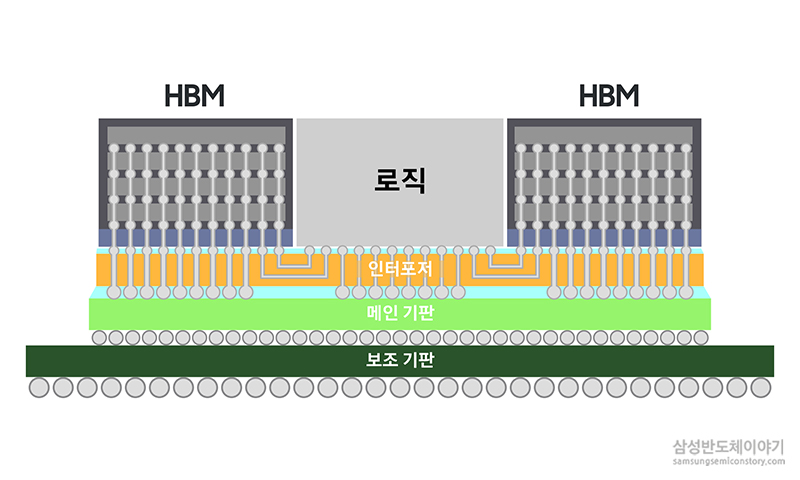

실리콘 인터포저 위에 CPU·GPU·HBM을 배치한 2.5D 패키징 기술이 적용된 삼성전자 H-CUBE.(사진=삼성전자)

패키징 기술이 각광을 받기 시작한 건 반도체 제조 공정이 미세화에 다다르면서입니다. 미세 공정의 기술적 한계를 극복하기 위해 칩과 칩을 연결하는 성능을 끌어 올리는 ‘첨단 패키징’ 기술이 개발됐고, 이것을 활용하는 것이 2나노, 3나노를 안정적으로 생산하는 시기를 기다리는 것보다 시간과 경제적인 측면에서 모두 절약할 수 있기 때문입니다. 특히 GPU, HBM 등 고성능 반도체 수요가 지난해부터 폭발적으로 일어나자 ‘첨단 패키징’은 반도체 시장에서 핵심 기술로 부상했습니다.

업계에서는 삼성전자가 첨단 패키징 기술력을 확보하면 SK하이닉스에 뒤처진 HBM 시장 점유율에서 앞서나갈 수 있을 뿐만 아니라, TSMC와도 시장 점유율 격차를 좁힐 수 있을 것이라고 봅니다.

HBM 시장을 양분하고 있는 삼성전자 SK하이닉스는 현재 생산하고 있는 HBM을 대부분 패키징까지 완료해 공급하는 형태를 취하지만, 차세대 기술인 HBM 6세대 HBM4부터는 성능·효율 등을 고려해 HBM과 GPU를 연결하는 패키징 공정은 첨단 기술력을 가진 업체가 하는 것이 유리할 것이라고 보기 때문입니다. 삼성이 첨단 패키징 기술 개발에 사활을 거는 이유입니다.

삼성전자는 HBM 6개 이상 탑재가 가능한 첨단 패키징 기술인 ‘I-Cube 2.5D’, ‘X-Cube 3D’를 확보, 더 나아간 기술 개발에 나섰습니다. 이를 위해 천안·온양 사업장 내 패키징 생산라인도 증설하고 있습니다.

반도체업계 관계자는 “삼성전자 인텔도 패키징 기술이 있지만 대부분 최종 공급받는 엔비디아나 애플이 TSMC의 패키징 공정을 활용한 최종 제품을 납품받기를 원한다”면서 “패키징 기술력이 앞으로 파운드리 시장점유율 장악에도 큰 영향을 미칠 것”이라고 말했습니다.

한편, 시장조사업체 트렌드포스에 따르면 지난해 3분기 기준 삼성전자 점유율은 12.4%로 TSMC(56.4%)와 45.5%포인트 차이가 났습니다. 이는 직전 분기 TSMC(56.4%), 삼성(11.7%) 격차 44.7%에서 더 벌어진 수치입니다.

삼성전자 화성사업장. (사진=삼성전자)

오세은 기자 ose@etomato.com